Purpose:

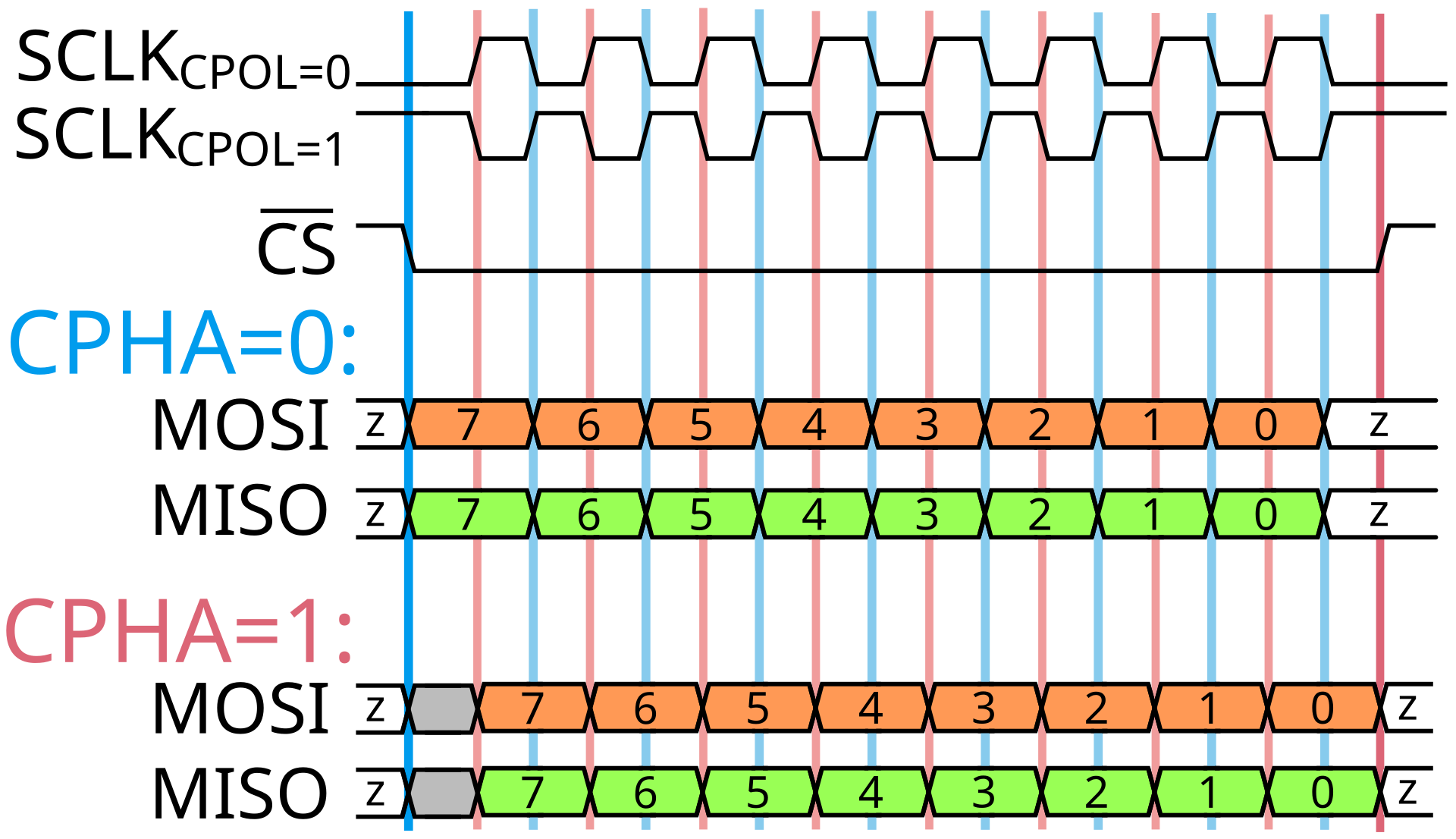

- Master configures clock frequency, polarity (CPOL), and phase (CPHA) to match the slave.

- CPOL & CPHA define when data is sampled and changed relative to the clock.

CPOL – Clock Polarity

- CPOL = 0: Clock idles LOW

- CPOL = 1: Clock idles HIGH

- (Can be inverted using a clock inverter if needed)

CPHA – Clock Phase

- Controls when data is captured/shifted within each clock cycle.

For CPHA = 0:

- First bit is output immediately when SS goes low.

- Subsequent bits output when clock returns to idle level.

- Sampling occurs on clock edge AWAY from idle.

For CPHA = 1:

- First bit is output on first clock edge after SS activates.

- Subsequent bits output when clock leaves idle level.

- Sampling occurs on clock edge RETURNING to idle.

Timing Note:

- MOSI and MISO are generally stable for half a clock cycle.

- Master and slave may choose different sample points within that half-cycle for flexibility.